China prepares a 2nm AI chip to end NVIDIA’s dominance. Your problem is how you are going to manufacture it

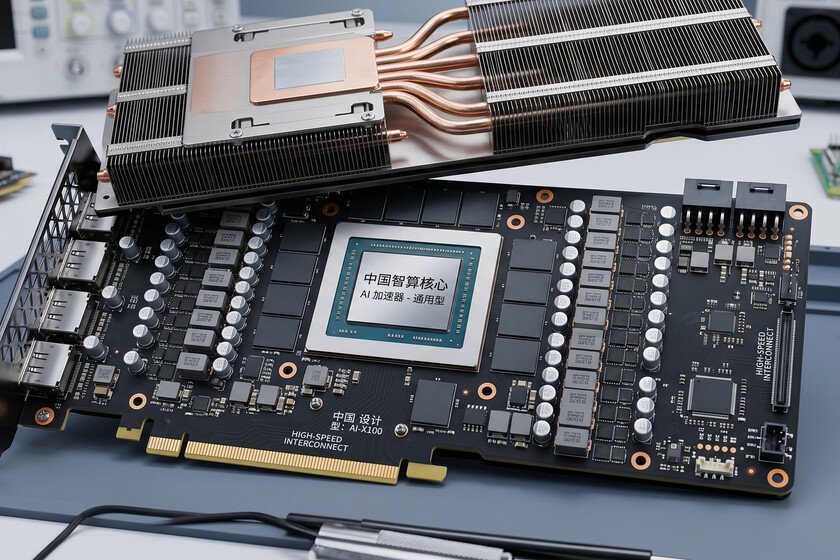

A new chip designer for artificial intelligence (IA) is preparing to take the field in China. And he intends to make a lot of noise. In fact, it is already doing so. It’s called Dishan Technology, and, according to SCMP, is already verifying the prototype of a 2nm AI GPU that uses a hybrid integration technology that combines FinFET and GAA transistors (Gate-All-Around). However, this is not the only thing that has emerged. According to Dishan Technology, this chip will be 40% more energy efficient than its predecessor and will be compatible with CUDA (Compute Unified Device Architecture), from NVIDIA. This latest technology brings together the compiler and development tools used by programmers to develop their software for NVIDIA GPUs, so if Dishan’s chip is really compatible it will be much easier to integrate it into facilities that already have GPUs from this American company. Although, as I mentioned above, Dishan already has a prototype of its chip, it will take another year or two to refine its technology enough to make large-scale manufacturing possible. Be that as it may, what has not been revealed is who is going to manufacture it. SMICthe largest Chinese semiconductor producer, can currently only manufacture 7nm chips using the multiple patterning. And TSMC, Intel and Samsung, which could produce it, will hardly do so in the current geopolitical context due to the demands of the US sanctions on China. We will see how Dishan Technology solves this challenge. China already has three “champions” in its AI chip ecosystem The country led by Xi Jinping you already have three alternatives very clear to NVIDIA. Although not as well-known as Huawei or Moore Threads, Cambricon Technologies is one of the companies specialized in designing GPUs for AI with the greatest growth potential. In fact, in August 2025 it received approval from the Shanghai Stock Exchange (China) to raise $560 million. He is allocating them to the design of four chips for training and inference of AI models, and also to the development of an alternative to CUDA. Moore Threads has developed several GPUs that rival advanced solutions from NVIDIA, AMD or Huawei On the other hand, Moore Threads has developed several GPUs for AI applications that, on paper, rival some of the advanced solutions that NVIDIA, AMD or Huawei have placed on the market. The cards MTT S4000 and MTT S3000 They are its most interesting proposals right now, although, curiously, the MTT S80 card also appears in its portfolio, a proposal for games and content creation that, according to Moore Threads itself, has a computing capacity of 14.4 TFLOPS in single-precision floating point operations. The other indispensable player in the Chinese AI chip industry is Huawei. His most ambitious proposal right now is the chip Ascend 950PRwhich aims to surpass the performance of the GPU NVIDIA H100. However, this Chinese company also launched its chips last year Ascend 910D and 920. This last solution is clearly intended to compete in the Chinese market with NVIDIA’s H20 GPU. Presumably at the end of 2026 it will launch its Ascend 950DT chip, and the Ascend 960 and 970 GPUs will arrive in 2027 and 2028 respectively. Image | Generated by Xataka with Gemini More information | SCMP In Xataka | TSMC acknowledges that it has considered taking its factories out of Taiwan. It’s impossible for a good reason. In Xataka | The looming bottleneck in AI is neither RAM nor gas: it’s that TSMC’s N3 node is absolutely saturated